## DAC/µP-Supervisor Combination Improves Analog I/O Reliability

Using a DAC and microprocessor supervisor, the reliability of the analog I/O can be improved in systems employing an industrial controller, a programmable logic controller (PLC), or in a data acquisition system. A simple application is shown on how to implement this function. The analog output is set to zero when it detects a microprocessor failure or undervoltage condition without the need of an optocoupler.

The analog control signals used in industrial controllers, programmable-logic controllers (PLCs), and data-acquisition systems include 0-5V, 0-10V,  $\pm$ 5V,  $\pm$ 10V, and 4-to-20mA current loops. For safety reasons, some analog-output modules employ optocouplers to electrically isolate the microprocessor ( $\mu$ P) and analog circuits. Also for reliability and safety, other systems require that the analog outputs reset to midscale or zero in response to a  $\mu$ P failure.

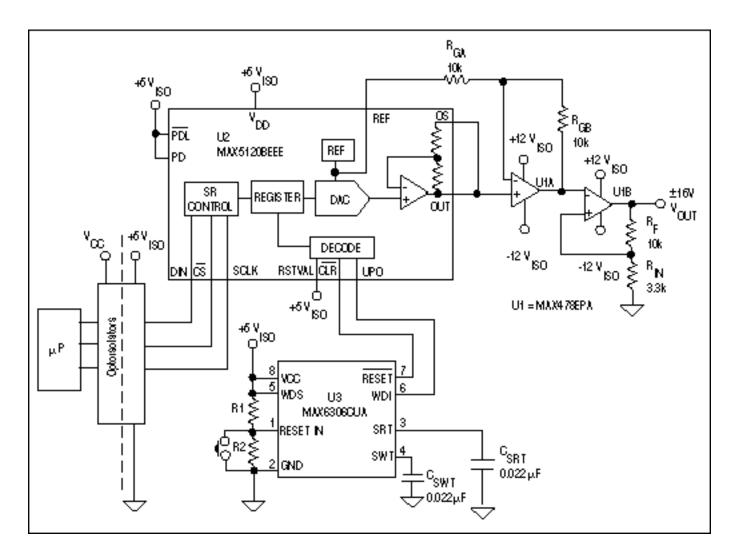

These requirements are met by the circuit in the figure, which monitors  $\mu P$  activity and sets the analog output to zero when it detects a  $\mu P$  failure or undervoltage condition. It also improves the mean time before failure (MTBF) by minimizing I/O pins at the  $\mu P$  and by eliminating an optocoupler.

When a failure occurs in the supply voltage or  $\mu$ P operation, this DAC (U2) and  $\mu$ P supervisor (U3) together produce a user-programmed default output (V<sub>OUT</sub>).

Three features enable the DAC (U2) to produce zero-scale resets: an asynchronous-reset input (CLR), a user-selectable reset-value input (RSTVAL), and a user-programmable output (UPO) for serial-interface setup. These built-in features also eliminate an optocoupler, minimize I/O pins at the  $\mu$ P, and lessen the need for external discrete circuitry. The  $\mu$ P supervisor (U1) includes a resistor-programmable reset-input threshold, a capacitor-programmable watchdog timer, and a reset-timeout period.

As DAC codes range from  $000_{HEX}$  to FFF<sub>HEX</sub>, the circuit output (V<sub>OUT</sub>) ranges from -10V to +10V. Op amp U1A is offset by the DAC's internal, 10ppm/° C precision bandgap reference, and the output op amp (U1B) is configured as a buffer with a gain of four. Output voltage for the circuit is

$VOUT = VREF x (G x NB/4096 - 1) x (R_F/R_{IN} + 1),$

where NB is the numeric value of the DAC's binary code,  $V_{REF}$  is the internal reference voltage, G is the gain of U1A, and  $R_F/R_{IN}$  is U1B's gain-resistor ratio.

U3 monitors the isolated supply voltage (V<sub>ISO</sub>) via its V<sub>CC</sub> pin. It also monitors  $\mu$ P activity via its WDI pin, and it generates a reset command via RESET. A resistor divider at RESET IN (pin 1) determines the reset-level threshold (V<sub>TH</sub>). Similarly, the reset timeout period (t<sub>RP</sub>) and watchdog timeout period (t<sub>WD</sub>) are determined by capacitor values at SRT and SWT. Connecting WDS to VCC extends t<sub>RP</sub> by a factor of 500. The following equations calculate values needed in the circuit:

$V_{RST} = V_{TH}(R1 + R2)/R2$ , where  $V_{TH} = 1.22V$  and  $V_{RST}$  is the adjustable reset threshold voltage.

$C_{RST} = t_{RP}/2.67$ , where  $C_{RST}$  is in pF.

$C_{SWT} = t_{WD}/2.67$ , where  $t_{WD}$  is in  $\mu$ s.

If V<sub>CC</sub> fails, or if the µP locks up and cannot toggle WDI, U3 asserts low on its RESET output, which resets U2 via its CLR input. This action resets U2's output to the condition set by RSTVAL (to midscale in this case, which produces 0V at V<sub>OUT</sub>). When U2 is being updated, its UPO output toggles U3's WDI at intervals less than the nominal watchdog timeout (t<sub>WD</sub> = 25 seconds, subject to tolerances on the capacitor and the ICs). Other devices to consider for the watchdog function are the MAX6316 series and the MAX6369 series, which offer fixed timeout periods in SOT23 packages.

The switch between U3's RESET IN and GND terminals allows the user to command an emergency shutdown. RESET pulls CLR high after the reset timeout ( $t_{RP} \cong 60$ ms), but the DAC output remains at midscale until updated. The DAC's unipolar and bipolar modes allow it to produce all the common analog-output control signals.

A similar version of this article appeared in the November 6, 2000 issue of *Electronic Design*.

D388, December 2000

## **More Information**

| MAX478:  | <u>QuickView</u> | <u>Full</u> | (PDF) | Data | <b>Sheet</b> | <u>Free</u> | Samples |

|----------|------------------|-------------|-------|------|--------------|-------------|---------|

| MAX5120: | <u>QuickView</u> | <u>Full</u> | (PDF) | Data | Sheet        | <u>Free</u> | Samples |

| MAX6306: | <u>QuickView</u> | <u>Full</u> | (PDF) | Data | <b>Sheet</b> | Free        | Samples |